# Parallel Algorithms on Configurable Hybrid UPC/MPI Clusters

K.Ganeshamoorthy

May 2010

# Parallel Algorithms on Configurable Hybrid UPC/MPI Clusters

A thesis submitted for the Degree of Master of Philosophy

K.Ganeshamoorthy University of Colombo School of Computing May 2010

### Declaration

The Thesis is my original work and has not been submitted previously for a Degree at this or any other University/Institute. To the best of my knowledge it does not contain any material published or written by another person, except as acknowledge in the text.

| Author's name ·····                             | Date ····· |

|-------------------------------------------------|------------|

| Signature · · · · · · · · · · · · · · · · · · · |            |

| Certified by: |                                                  |                   |

|---------------|--------------------------------------------------|-------------------|

| Supervisor 1  | Name:                                            | Date:             |

|               | Signature: · · · · · · · · · · · · · · · · · · · |                   |

|               |                                                  |                   |

|               |                                                  |                   |

| Supervisor 2  | Name:·····                                       | Date: · · · · · · |

|               | Signature: · · · · · · · · · · · · · · · · · · · |                   |

To my loving mother, Sinnathangam . . .

## Table of Contents

| Τa            | able o                                  | of Contents                                                                                                                                                                                                                                                                                                                                                                                                                   | iv                                                                                                |

|---------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| $\mathbf{Li}$ | st of                                   | Tables                                                                                                                                                                                                                                                                                                                                                                                                                        | vii                                                                                               |

| Li            | st of                                   | Figures                                                                                                                                                                                                                                                                                                                                                                                                                       | viii                                                                                              |

| $\mathbf{A}$  | bbrev                                   | viations                                                                                                                                                                                                                                                                                                                                                                                                                      | ix                                                                                                |

| $\mathbf{A}$  | bstra                                   | let                                                                                                                                                                                                                                                                                                                                                                                                                           | x                                                                                                 |

| A             | cknov                                   | wledgment                                                                                                                                                                                                                                                                                                                                                                                                                     | xii                                                                                               |

| 1             | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | <b>voduction</b> Background         Motivation         Aims and Objectives         Summary of Main Results         Thesis Outline                                                                                                                                                                                                                                                                                             | <b>1</b><br>1<br>3<br>3<br>4<br>6                                                                 |

| 2             | Clui<br>2.1<br>2.2                      | ster Computing         Background         Distributed Memory (DM)         2.2.1         Message Passing Interface (MPI)         2.2.2         Parallel Virtual Machine (PVM)         2.2.3         Theoretical Chemistry Group Message Passing System<br>(TCGMSG)                                                                                                                                                             | 7<br>7<br>8<br>9<br>9<br>9                                                                        |

|               | <ul><li>2.3</li><li>2.4</li></ul>       | 2.2.4 AVS/Express Parallel EditionDistributed Shared Memory (DSM)2.3.1 TCP-Linda2.3.2 Unified Parallel C (UPC)2.3.3 Intel® Cluster OpenMP* (CLOMP)2.3.4 CORSODM Vs. DSM - Comparative Performance on a HPC Cluster2.4.1 Performance Comparison of Treadmarks, PVM, and MPI2.4.2 Performance Comparison of UPC, CORSO, and MPI2.4.3 Performance Comparison of CLOMP and OpenMP2.4.4 Performance and Flexibility of MPI and UPC | $     10 \\     11 \\     12 \\     12 \\     13 \\     14 \\     15 \\     17 \\     18 \\     $ |

| 3             | <b>Ext</b><br>3.1                       | racting Parallelism from a Hierarchy of Processing Levels in a ClusterMixed Mode Approach for HPC Cluster Programming.3.1.1Mixed mode MPI/OpenMP algorithms3.1.2Mixed mode MPI/pthreads and MPI/cache algorithms                                                                                                                                                                                                              | <b>20</b><br>20<br>21<br>23                                                                       |

| <b>4</b> | Sha | llow Water Model on a Cluster 2                                                    | 5       |

|----------|-----|------------------------------------------------------------------------------------|---------|

|          | 4.1 | Shallow Water Equations                                                            | 25      |

|          | 4.2 |                                                                                    | 25      |

|          |     | 4.2.1 Parallel Simulations of Tsunami Effect                                       | 25      |

|          |     | 4.2.2 Parallel implementation of a highly nonlinear Boussinesq equation model      |         |

|          |     |                                                                                    | 27      |

|          |     | 4.2.3 Implicit Parallel FEM Analysis of Shallow Water Equations 2                  | 28      |

|          | 4.3 |                                                                                    | 29      |

|          | 4.4 |                                                                                    | 81      |

|          | 4.5 | о́ о́                                                                              | 84      |

|          |     |                                                                                    | 86      |

|          |     | · -                                                                                | 86      |

|          |     | · -                                                                                | 86      |

|          |     |                                                                                    | 87      |

|          |     |                                                                                    |         |

| <b>5</b> | Art |                                                                                    | 9       |

|          | 5.1 | Parallelization of Feed-Forward ANNs                                               | 13      |

|          | 5.2 | Related Work                                                                       | 15      |

|          |     | 5.2.1 Mapping of a Multilayered ANN onto a Network of Workstations 4               | 15      |

|          |     | 5.2.2 Substituting Parallel Matrix Multiplication in the Training Phase of         |         |

|          |     | Back-propagation ANNs                                                              | 6       |

|          |     | 5.2.3 Parallel ANN Training Algorithms for Finance Applications 4                  | 17      |

|          |     | 5.2.4 Massively Parallel ANNs                                                      | 18      |

|          |     | 5.2.5 Factors Affecting the Training of a Distributed Back-propagation algorithm 4 | 8       |

|          | 5.3 | Design of a Parallel Algorithm                                                     | 19      |

|          |     | 5.3.1 Batch update back-propagation with parallel matrix multiplication (NHP       |         |

|          |     | with BBP) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 5                           | 51      |

|          |     | 5.3.2 Hybrid partition with batch update back-propagation and matrix mul-          |         |

|          |     |                                                                                    | 55      |

|          |     | 5.3.3 Hybrid partitioning approach with incremental update back-propagation        |         |

|          |     |                                                                                    | 60      |

|          | 5.4 | 1                                                                                  | 51      |

|          |     |                                                                                    | 52      |

|          |     | v i                                                                                | 53      |

|          |     |                                                                                    | 53      |

|          |     | 5.4.4 Analysis of Results                                                          | 66      |

| 6        |     | Configurable DM/DSM Cluster 6                                                      | 8       |

| 0        | 6.1 |                                                                                    | 58      |

|          | 6.2 |                                                                                    | 59      |

|          | 0.2 | 8 8                                                                                | 71      |

|          |     |                                                                                    | -<br>73 |

|          | 6.3 |                                                                                    | 76      |

|          | 0.5 |                                                                                    | 0       |

| <b>7</b> | Per | formance of the Shallow Water Model on the Configurable Cluster 7                  | 7       |

|          | 7.1 | Review of MPI, UPC, and UPC/MPI for                                                |         |

|          |     |                                                                                    | 7       |

|          | 7.2 | 0                                                                                  | 78      |

|          |     |                                                                                    | 78      |

|          |     |                                                                                    | 78      |

|          |     | 7.2.3 Meta expressiveness                                                          | 79      |

| 8  | Conclusion and Future Work                                                            | 80                                                                       |

|----|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Re | eferences                                                                             | 82                                                                       |

| W  | eb References                                                                         | 89                                                                       |

| Α  | Theory of Shallow Water ModelsA.1Introduction                                         | I<br>I<br>II<br>III<br>III<br>IV                                         |

| В  | Matrix Multiplications         B.1       Cache layer matrix multiplication algorithms | V<br>VI<br>VI<br>VI<br>VI<br>VI<br>VI<br>VII<br>VII<br>VII<br>VII<br>VII |

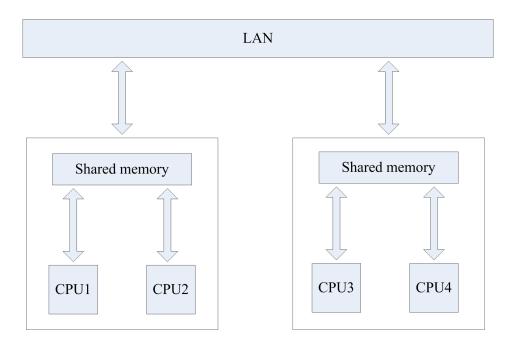

| С  | Hardware Configurations         C.1       Multiprocessors                             | IX<br>IX<br>IX<br>X                                                      |

| D  | <ul> <li>D.1 The Multi-layer ANN</li></ul>                                            | XII<br>XIII<br>XIII<br>XV<br>XV<br>XV<br>/III                            |

# List of Tables

| 4.1 | Run time in seconds (wot - without thread; wt - with thread) $\ldots \ldots \ldots \ldots$ | 37    |

|-----|--------------------------------------------------------------------------------------------|-------|

| 4.2 | Running time factors.                                                                      | 37    |

| 5.1 | Artificial neural network architectures                                                    | 50    |

| 5.2 | Mean training time in seconds for $ANN_1$ using MPI                                        | 64    |

| 5.3 | Mean training time in seconds for $ANN_2$ using MPI                                        | 64    |

| 5.4 | Mean training time in seconds for $ANN_3$ using MPI                                        | 65    |

| 5.5 | Mean training time in seconds for $ANN_1$ using TCP-Linda                                  | 65    |

| 5.6 | Mean training time in seconds for $ANN_2$ using TCP-Linda                                  | 65    |

| 5.7 | Number of MPI functions called at training time                                            | 66    |

| 7.1 | Average run time in seconds for the shallow water model with $(4 \times 3)$ grid scheme on |       |

|     | Upplanka cluster                                                                           | 77    |

| E.1 | Run time in seconds (wot - without thread; wt - with thread) were obtained from the        |       |

|     | Monolith high performance cluster                                                          | XVIII |

| E.2 | Run time in seconds (wot - without thread; wt - with thread) were obtained from the        |       |

|     | Monolith high performance cluster                                                          | XVIII |

| E.3 | Run time in seconds were obtained from the Upplanka high performance cluster $~$ . $~$ .   | XIX   |

# List of Figures

| 3.1 | Mixed mode programming model on HPC cluster Ref. (Wu et al., 2002)                                                                                        | 21  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

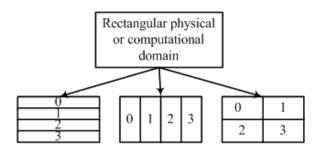

| 4.1 | Three possible ways of decomposing a rectangular domain. The numbers in the sub-                                                                          |     |

|     | domains represent the processor number.                                                                                                                   | 31  |

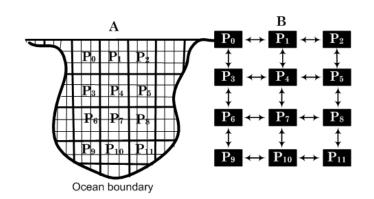

| 4.2 | (A) Overview of the unstructured grid and assignment of worker nodes to sub-domains.                                                                      |     |

|     | (B) Arrows indicate the inner-worker communication.                                                                                                       | 32  |

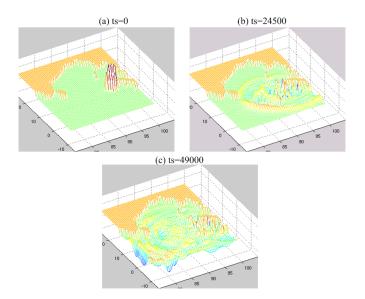

| 4.3 | Linear shallow water wave profiles at three different time-steps (ts) calculated using                                                                    |     |

|     | 48 processors                                                                                                                                             | 32  |

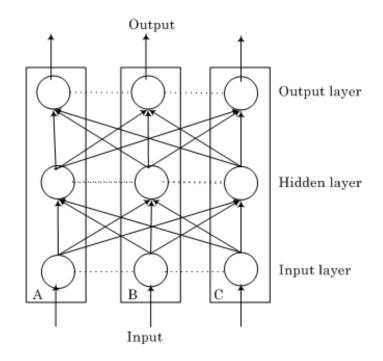

| 5.1 | Vertical partition of an ANN (Sudhakar & Murthy, 1998)                                                                                                    | 42  |

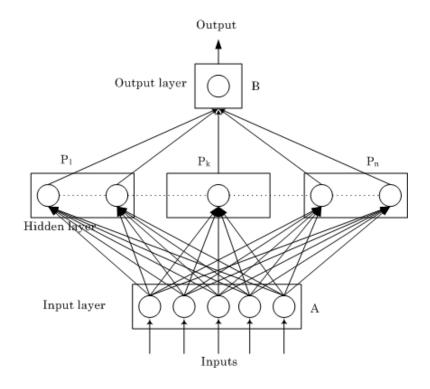

| 5.2 | Hybrid partition of an ANN (Suresh et al., 2005)                                                                                                          | 42  |

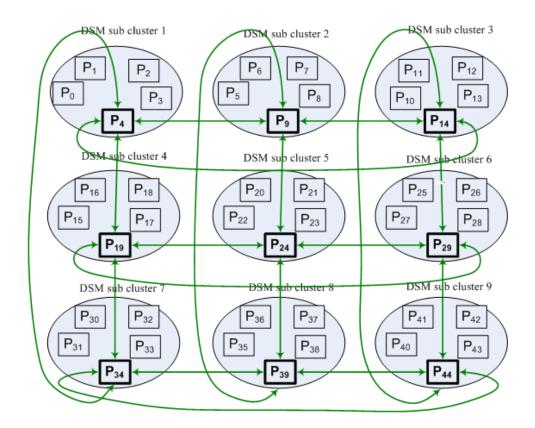

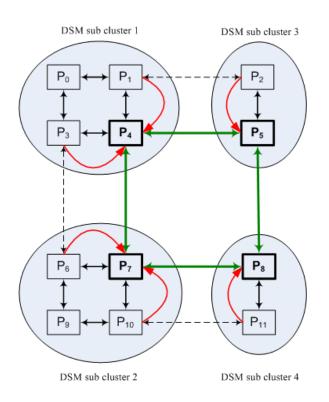

| 6.1 | $\operatorname{DSM}$ sub clusters interconnected by MPI using two-dimensional toroidal topology                                                           | 69  |

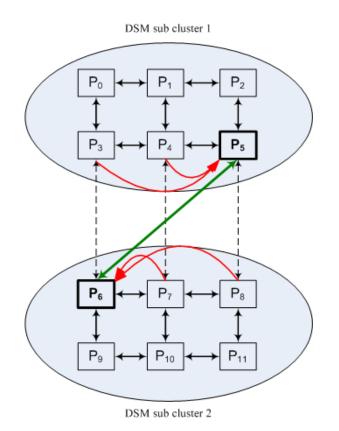

| 6.2 | A 12-node cluster is configured as two DSM sub clusters interconnected by MPI                                                                             |     |

|     | $(configuration-1). \ldots \ldots$ | 70  |

| 6.3 | A 12-node cluster is configured as four DSM sub clusters interconnected by MPI                                                                            |     |

|     | $(configuration-2). \ldots \ldots$ | 71  |

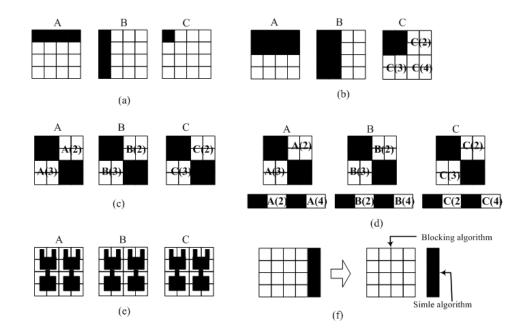

| B.1 | Pictorial representation of cache level matrix multiplication algorithms (Wu et al.,                                                                      |     |

|     | 2002)                                                                                                                                                     | V   |

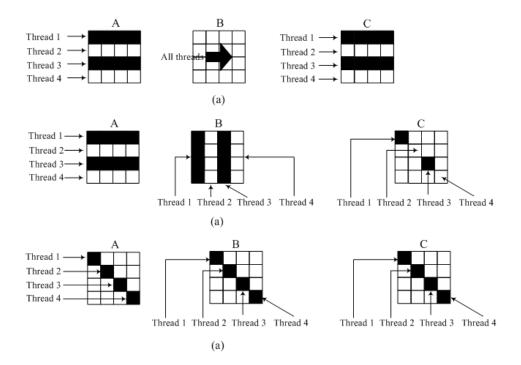

| B.2 | Pictorial representation of shared memory matrix multiplication algorithms (Wu et                                                                         |     |

|     | al., 2002)                                                                                                                                                | V   |

| C.1 | Communication between threads on a distributed memory computer (Buchau et al.,                                                                            |     |

|     | 2008)                                                                                                                                                     | Х   |

| C.2 | Communication between threads on a shared memory computer (Buchau et al., 2008).                                                                          | Х   |

| C.3 | The architecture of the CMP system with up to 16 processors. The core organizations                                                                       |     |

|     | for the cache-based and streaming models are shown on left and right side respectively                                                                    |     |

|     | (Leverich et al., 2007)                                                                                                                                   | XI  |

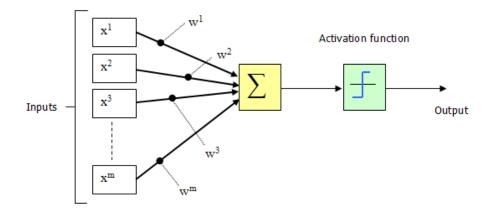

| D.1 | The perceptron.                                                                                                                                           | XII |

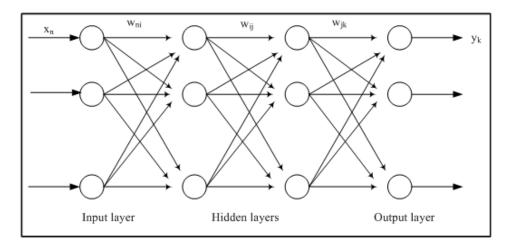

| D.2 | A four-layer feed-forward ANN.                                                                                                                            | XII |

## Abbreviations

- 1. ANN Artificial Neural Network

- 2. BBP Batch Back-Propagation

- 3. CLOMP- Cluster OpenMP

- 4. CMP Chip Multi Processors

- 5. DM Distributed Memory

- 6. DSM Distributed Shared Memory

- 7. HP Hybrid Partition

- 8. HPC High Performance Computing

- 9. IBP Incremental update Back-Propagation

- 10. MLP Multi-Layer Perceptron

- 11. MP Message Passing

- 12. NHP Non Hybrid Partition

- 13. PVM Parallel Virtual Machine

- 14. SMP Symmetric Multi Processors

- 15. TCGMSG Theoretical Chemistry Group Message passing System

- 16. UPC Unified Parallel C

- 17. VP Vertical Partition

- 18. VSM Virtual Shared Memory

### Abstract

High performance computing (HPC) applications have increasingly tended to use "off the shelf" commodity clusters of workstations as their executing platform, in the last decade due to their generic nature and low cost. The typical cluster of nodes, as well known, is a distributed memory structure, whose programming paradigm of message passing is well established.

This thesis presents a study of the impact of hybrid memory architectures composed of distributed memory and distributed shared memory, within a multi-processor cluster on the design of parallel algorithms. The thesis proposes a novel configurable virtual cluster arrangement interconnected by message passing links as a programming metaphor for parallel algorithm design. The study uses solution of parallel numerical algorithms and parallel back-propagation neural network algorithms as case studies. The parallel implementation of the shallow water equations to model a Tsunami is emphasized.

In the tsunami model, a rectangular array of data is partitioned into sub-domains, namely a four by three grid scheme and an eight by six grid scheme which are then used for the parallel implementation. In the preliminary study of hybrid memory architectures, four versions of the parallel algorithm for each grid scheme are used: distributed memory without threads, distributed memory with threads, distributed shared memory without threads, and distributed shared memory with threads. Experiments are realized using the Message Passing Interface (MPI) library, C/Linda, and the Linux pthreads. Subject to the availability of memory, the distributed shared memory version without threads performs best, but as the task is scaled up, the threaded version becomes efficient in both distributed memory and distributed shared memory implementations.

In the case of parallel algorithms for neural network training, the neural network is partitioned into sub neural networks by applying a hybrid partitioning scheme. Therefore, each partitioned network is evaluated as a matrix multiplication. Three different sizes of neural networks were used and exchange rate prediction was used as the reference problem. Parallel implementations for each of the distributed memory and distributed shared memory scenarios were obtained. The partitioned, matrix multiplication had the fastest execution time, and the MPI implementation was always faster than the TCP-Linda equivalent. The configurable hybrid cluster scheme was implemented as two UPC/MPI sub cluster configurations where, in the first configuration, configuration-1, twelve computing nodes are partitioned into two equal sized DSM sub clusters, and in the second configuration, configuration-2, twelve computing nodes are partitioned into four DSM sub clusters. UPC is used for intra sub clusters while MPI is used for inter-sub-cluster communication. The shallow water model was implemented on each of these configurations.

The parallel algorithm for the uniform DSM implementation exhibits a moderately better performance than either of the two parallel algorithms for the UPC/MPI hybrid cluster configurations while these two parallel algorithms individually exhibit an overall better performance than the parallel algorithm for the uniform DM architecture, in terms of running time. Configuration-1 exhibits a moderately better performance than that for configuration-2. As the number of computing nodes per DSM sub cluster decreases, the overall performance approaches that of a DM.

A cluster with a large number of computing nodes when configured as a UPC/MPI hybrid sub cluster provides algorithmic timing values faster than that for the pure DM programming model. Moreover, the set of DSM sub clusters can be configured into arbitrary topologies such as a two dimensional toroidal mesh type topology, enabling a more flexible programming approach and the possibility of reusing well known algorithm designs for high performance applications.

## Acknowledgment

The work described in this thesis was carried out while I was reading for my Master of Philosophy Degree at the Department of Computation and Intelligent Systems, University of Colombo School of Computing (UCSC).

I would especially like to thank Dr D N Ranasinghe, Senior Lecturer in Computer Science and Deputy Director of the UCSC, for his constant encouragement and support in the development of this research, particularly for the many stimulating and instructive discussions we had on Parallel Algorithm Developments.

I am also extremely grateful to Mr. Malik Silva, Lecturer in Computer Science at the UCSC for his assistance provided in various stages of this research.

I also wish to thank all my colleagues, both past and present, of the UCSC for their assistance during the progression of this research, with special emphasis to Dr Mahen Jayawardena, Lecturer in Computer Science at the UCSC and Mr Chaminda Ratnasinghe.

I also wish to thank the continuous support and encouragement provided my family members in making this research a success.

This research was performed using computational resources at the National Supercomputer Centre, Linköping University, Sweden, and the computational resources of University of Colombo School of Computing. Partial funding was provided by the National Science foundation, Sri Lanka (Grant No. RG/2005/FR/07) and by SPIDER, the Swedish programme of ICT for developing Regions, the latter especially for the setting up of the cluster infrastructure.

# Chapter 1 Introduction

### 1.1 Background

Computer architects and application developers have attempted to extract the maximum performance out of emerging CPU designs and programming paradigms in the last 3-4 decades in order to run high performance applications. Processor architectures have improved dramatically over the years in line with Moore's Law, which predicts a doubling of power every 18 months [WWW 21]. With the current fabrication densities, it is now possible to have many thousands of cores per CPU. This has been one direction of advancement. The other has been to extract more computational power using the MIMD philosophy, i.e. commodity cluster computing (Hung & Adeli, 1994). Together, these two approaches provide a formidable computing power in the modern era. This trend makes parallelization of software not optional but indispensable (Buchau et ai., 2008; Leverich et al., 2007; Cheng et al., 2006). However the weak point in the whole picture has been the absence of proper tools and programming paradigms to extract the emerging power of parallel architectures.

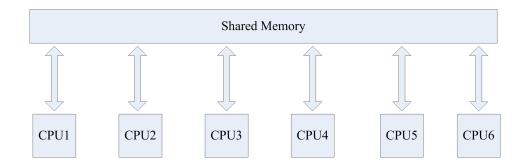

Typically a modern computer consists of one or more multicore CPU's with shared memory. This means that all CPU's access the common memory. The software is designed in such a way that a single process is split into multiple threads. Ideally, one thread per processor should be assigned. Multithreading is supported by most compilers with the well-known OpenMP [WWW 08] standard. OpenMP is independent of platform and operating system. A very important advantage of OpenMP is that load distribution is done dynamically during runtime. OpenMP is a widely used shared memory programming approach (Smith & Bull, 2001; Blikberg, 2003; Wong & Rendell, 2007).

Parallel computing on a commodity computing cluster has been gaining more attention in recent years due to its cost effectively compared to conventional supercomputers. Furthermore together with high speed general purpose switched networks, powerful clusters are narrowing the performance gap between clusters and supercomputers (Sudhakar & Murthy, 1998; Suresh As no physical memory is shared between CPU's in a HPC cluster, all communication between processes in such a system must be performed by sending and receiving messages over the network. Currently, the prevailing programming model for parallel computing on HPC cluster is message passing. Libraries such as MPI [WWW 01], (Werstein et al., 2003; Smith & Bull, 2001; Lotrič & Dobnikar, 2005; Bova et al., 2000), PVM [WWW 02], (Werstein et al., 2003; Araiijo et al., 2003; Mattson, 1995), TCGMSG [WWW 03], (Mattson, 1995), and AVS/Express [WWW 04] have been developed at different research institutions as solutions. MPI is very popular and allows the software developer full control over the execution of parallel program.

The latest popular distributed shared memory (DSM) systems (Shan et al., 2001; Werstein et al., 2003, Gansterer & Zottl, 2005; Wong & Rendell, 2007), [WWW 05], also known as virtual shared memory (VSM) systems [WWW 06], (Mattson, 1995) or partitioned global address space (PGAS) systems [WWW 05], [WWW 14], (Husbands & Yelick, 2007), provide a shared memory abstraction on top of message passing in a HPC cluster. This is a very useful abstractions for programmers who are familiar with shared memory programming. Libraries such as TCP-Linda<sup>®</sup> [WWW 06], (Mattson, 1995), Unified Parallel C (UPC) [WWW 14], (Husbands & Yelick, 2007), TreadMarks (Keleher et al., 1994), SCASH (Harada et al., 1999), Co-ORdinated Shared Objects (CORSO) [WWW 15] and Cluster OpenMP\* for Intel® C++ Compiler [WWW 07] have been developed at different research institutions to address this model of programming. A parallel application programmer can write the parallel program as if it is executing in a shared memory multi-processor and access shared data with general *read* and write operations. The software developer leaves the distributed shared memory system to handle the underlying message passing. It is easier to program with the shared memory paradigm, especially when the algorithm is very complicated, because the programmer can concentrate more on the algorithm design rather than on explicitly moving data among processes (Shan et al., 2001; Werstein et al., 2003; Gansterer & Zottl, 2005; Keleher et al., 1994).

For an HPC cluster with multi-processor nodes parallelization is more complicated. Here, CPUs will share local memory on each node, while the overall memory is distributed among the computing nodes. The system requires a mixed mode programming model (Wu et al., 2002; Smith & Bull, 2001). While MPI and TCP-Linda can be used for communication between global nodes in the distributed memory environment (or in a distributed shared memory environment derived from the DM), inside each MPI process and within each TCP-Linda process POSIX threads can be used in order to extract further parallelism, resulting in a mixed mode programming model.

Due to the evolving CPU architectures from single processor nodes to symmetric multiprocessors and multi-core CPU's in recent times, the processing hierarchy of a generic cluster has opened up new approaches for the development of novel parallel programming models.

A flexible programming model, which is scalable and can consolidate a wide hierarchy of shared and distributed memory architectures within a cluster with nodes having single to multi CPU's each with large number of possible cores, is sought after by researchers. Our work is an attempt in that direction.

#### **1.2** Motivation

Computable tasks can be classified mainly in two different major views, computationally intensive problems and communicative intensive problems. Parallel programming approaches using a divide and conquer strategy are more efficient when the computation to communication ratio is high. This has to be considered in the master-slave computation prevalent in typical cluster computing. Among the programming models widely used on clusters, message passing is a model that arises directly from the architecture of distributed memory multiprocessors and networks of workstations (Smith & Bull, 2001; Sudhakar & Murthy, 1998; Suresh et al., 2005). A distributed shared memory programming model is more efficient when message passing between computing nodes is less, i.e. smaller number of shared variables are used to communicate between computing nodes [WWW 07]. Therefore, one of the motivations of this study is to analyze the relevance of the programming models to two classes of real world problems. The studies done so far (Werstein et al., 2003; Gansterer & Zottl, 2005) show that DSM implementations always have higher overhead than their DM counterpart irrespective of the type of task. We reexamine this aspect here. Another aspect we will examine here is the behavior of the mixed mode programming model under task and architecture scaling. This forms the hypothesis that there are alternative programming models, that could exploit the hierarchy of processing capabilities found in a cluster more effectively, even for a restricted class of computational tasks. Finally, the insights gained in the study might have interesting implications for emerging large scale multi-core based CPU programming as well.

#### **1.3** Aims and Objectives

The objective here is to evaluate the effects of the programming model on scalability of the shallow water computational model and for the training of a back-propagation neural network.

The execution environment is a multinode cluster. Computing the wave propagation in the tsunami model, where the entire ocean is the solution domain, is challenging, both due to the huge amount of computation needed and due to the fact that different physics applies in different regions (Cai & Langtangen, 2007). Training of neural network using back-propagation is a computationally intensive task, requiring millions of floating point multiplications (Yoon et al., 1990; Sudhakar & Murthy, 1998; Suresh et al., 2005; Long & Gupta, 2008). Further, large amounts of memory is required for neural networks (Novokhodko & Valentine, 2001; Babii, 2007).

Further, as mentioned in section 1.2, we wish to study the impact of memory architectures associated with distributed memory and distributed shared memory in the extraction of multiple levels of parallelism, for the solution of numerical algorithms and for the training of neural network using back-propagation algorithms.

#### 1.4 Summary of Main Results

In the tsunami model, two partition schemes, a four by three  $(4 \times 3)$  grid scheme and a eight by six  $(8 \times 6)$  grid scheme, have been applied to partition the data into sub-domains. The two grid schemes have been used for the parallel implementation of this model. We present four parallel algorithms under each grid scheme: (i) pure TCP-Linda; (ii) mixed mode TCP-Linda/pthreads; (iii) pure MPI; and (iv) mixed mode MPI/pthreads. The first two parallel algorithms belong to distributed shared memory approach and the last two algorithms belong to distributed memory approach.

In both threading and non-threading programming environments, the parallel algorithms for the distributed shared memory exhibit better performance than the algorithms for distributed memory, for both grid schemes. Though the distributed shared memory implicitly passes messages at the lower level, the replication management subsystem have been optimized in TCP-Linda compared to MPI [WWW 06], to yield better performance.

In the  $(4 \times 3)$  grid scheme, in both scenarios for distributed memory and distributed shared memory, non-threading algorithms exhibit better performance than threading algorithms. In contrast to previous instance, in both algorithms for distributed and distributed shared memory, the threading algorithms exhibit better performance than non-threading algorithms.

Among the parallel variations not using threads in both memory architectures, the  $(4 \times 3)$

grid scheme shows better performance than  $(8 \times 6)$  grid scheme. This is due to the ratio of computation time to communication overhead decreasing faster for domains with smaller size. However, when the task is scaled up, say up to  $(8 \times 6)$  grid system, due to the smaller subdomain sizes aligning with the available memory in the node, the threaded versions become more efficient in both MPI and TCP-Linda implementations. In both threading and nonthreading environments, the TCP-Linda version exhibits better performance than the MPI version. This result is significant as none of the literature reports a class of task that gives better timing performance under DSM than DM.

Three parallel back-propagation neural network training algorithms have been used to predict the exchange fluctuation rate as determined by demand and supply conditions in the foreign exchange market, under each of the memory systems, distributed memory and distributed shared memory. The first algorithm uses a hybrid partitioning approach and without using batch back-propagation. The second algorithm uses the batch back-propagation approach and fast parallel matrix multiplication for weight iterations. Finally, the third algorithm uses the hybrid partitioning approach and uses batch back-propagation approach within each sub neural network with fast matrix multiplication for weight iteration.

For all three neural network configurations, the parallel algorithms under the distributed memory architectures show vastly superior timing than distributed shared memory parallel algorithms. The reason being that according to the code, the neural network assigned to each TCP-Linda process is read and is written back from/to the distributed shared memory, for all training tasks. These read and write operations are implemented in TCP-Linda by *in* and *out* operations. The *in* and *out* operations take considerable time to act on the user defined data types, such as "struct". In the TCP-Linda program, the optimum number of processors have been dynamically assigned, even though the running time is very high. The third parallel algorithm is more efficient than the other two parallel algorithms in either of the memory architectures.

Since the communication time per training epoch for a given input pattern is higher than the time for computations, there is little advantage on the use of threads as a programming tool, in the neural network scenario.

### 1.5 Thesis Outline

The thesis is organized as follows: In Chapter 2, we elaborate on the cluster computing environments. Mostly focused on programming models such as message passing and distributed shared memory and on performance comparison among these two programming models. Mixed-mode algorithms which are used to exploit the parallel hierarchy, are reviewed in Chapter 3. In Chapter 4, shallow water equations to model the tsunami effect are described. Three parallel algorithms for the training of artificial neural networks using back-propagation on a cluster are analyzed in Chapter 5. In Chapter 6, a configurable hybrid DM/DSM cluster environment is explained and its implementation described. Analysis of results for the shallow water equations to model the tsunami effect on the proposed configuration is discussed in Chapter 7. Finally, Chapter 8 gives the conclusion of our research and future directions.

# Chapter 2 Cluster Computing

### 2.1 Background

Cluster computing refers to approach in building up an execution environment consists of two or more computers via a high speed network in order to take advantage of the cumulative parallel processing power of those computers [WWW 17] (Shan et al., 2001; Aung et al., 2005). The recent advances in high speed networks and improved microprocessor performance are making clusters an appealing vehicle for cost effective parallel computing. Clusters built using commodity hardware and software components are playing a major role in redefining the concept of super computing (Aung et al., 2005).

Cluster computing is used as a relatively low-cost form of parallel processing for scientific and other large scale applications that lend themselves to parallel operations. Most important applications include computational simulations of weather, simulations of material physics, simulations of molecule dynamics, flow computing, etc. (Ganeshamoorthy et al., 2009; Ganeshamoorthy et al., 2007; Buchau et al., 2008; Thomas, 1994).

The trend in parallel computing is to move away from specialized platforms to cheaper, general purpose systems consisting of loosely coupled components built up from single or multiprocessor workstations or PCs. This approach has a number of advantages including that of being able to build a platform for a given budget, which is suitable for a large class of applications and workloads.

Cluster computing has become more popular in recent years as the power of commodity processors has approached that of workstation processors. The standardization of network hardware and software protocols has also improved the viability of low cost cluster computing. The complexity in the high performance applications and the need for ever more computational power has kept pace with one technological important in processors and network technologies, thereby making able to design clusters that can meet the computational demand. However, not all problems are amenable to cluster solutions. As stated in Amdahl's Law (Hill & Marty, 2008) the task should have a high fraction of inherent parallelism to be of any use when parallelized. Depending on the communication costs of the algorithm used to solve the problem, employing a cluster may bring zero or negative benefits. On the other hand, there is a wide class of problems which can be cheaply and effectively solved using clusters (Ganeshamoorthy & Ranasinghe, 2008; Cai & Langtangen, 2007; Suresh, 2005).

Within the limitations of the cluster framework, there are other benefits of clustering. For example, clusters offer greater scalability than traditional symmetric multiprocessing (SMP) computers. With additional hardware, the performance of the cluster can increase substantially (Hope & Lam, 2008).

Generally, the target operating system used in a cluster computing machine is Linux being open and freely available. The Symmetric Multiprocessor (SMP) feature is also recognized by most Linux distributions.

Existing software tools generally take one of two major approaches to parallel program execution: message passing or virtual shared memory computing [WWW 06]. These two paradigms differ in many ways, but most importantly in their approaches to storing the data that is shared among the various components of a parallel program and to making the data available to the components that need it as the program runs.

Cluster computing systems can with the help of suitable middleware, provide additional services to users. We can use the queuing management software, Portable Batch System (PBS), to manage jobs submitted by different users [WWW 16]. This forms the basis of Grid Computing (Ouyang et al., 2008).

### 2.2 Distributed Memory (DM)

Message passing is a model that arises directly from the architecture of distributed memory multiprocessors and networks of workstations; the best known examples are MPI [1], a widely implemented standard message passing system, PVM [WWW 02], a library developed around the concept of a virtual machine that provides a single logical machine across the distributed memory cluster, TCGMSG [WWW 03], a toolkit for writing portable parallel programs using a message passing model, and AVS/Express Parallel Edition [WWW 04], a framework for parallel computation on multi-processor and networked computers.

In this approach, each program datum belongs to some specific process, and it must be explicitly transmitted to any other processes that need it as the program progresses. Sending and receiving a single such message requires many steps by both the transmitting and receiving processes, and parallel programs built with message passing systems typically send many, many messages in the course of execution.

The above message passing libraries may require users to have a deep understanding in parallelizing their applications. Doing so will help improve the performance of running parallel applications on the cluster computing system. Unfortunately, training the users to achieve such a goal is costly.

#### 2.2.1 Message Passing Interface (MPI)

There are many different versions of MPI libraries available with prominent examples being MPICH2 [WWW 18], LAM/MPI [WWW 19], and Open MPI [WWW 20]. As a result of this dominance, vendors of cluster network components often invest considerable time and effort in developing high performance MPI implementations that can make best use of their underlying hardware. MPI is very powerful and allows the software developer full control over the execution of program. Nevertheless, MPI has some disadvantages. The complete program must be parallelized and not only time-consuming parts. In practice, this is often ignored and some parts of the program are executed on all nodes with the same data. Then, conflicts in file access or the like must be avoided. The main disadvantage is that data exchange between the processes must be implemented by the software developer and load balance must be provided, too. This makes programming for message passing paradigm hard, especially for large applications with complex data structures (Werstein et al., 2003; Smith & Bull, 2001; Lotrič & Dobnikar, 2005).

#### 2.2.2 Parallel Virtual Machine (PVM)

PVM was originally developed at Oak Ridge National Laboratory and the University of Tennessee. The PVM library is developed around the concept of a virtual machine that provides a single logical machine across the distributed memory cluster. It is freely distributed with Linux RedHat, providing a structure where a great variety of programs can be officially developed using the available hardware. PVM transparently handles all message routing, data conversion, and task scheduling across a network of incompatible computer architectures. PVM enables a collection of heterogeneous computer systems to be viewed as a single parallel virtual machine. A virtual machine is associated with the user that starts it. The virtual machine exists as a daemon on each of the nodes in the cluster. Processes communicate via the daemon, which is responsible for handling communication between nodes. With PVM, resource management is dynamic. PVM includes a console program to manage the virtual machine. The console allows nodes to be added to or deleted from the virtual machine and provides process management utilities. PVM provides diversity of applications in parallel programming mainly because it supports the languages: C, C++, and Fortran. The planning of buffers and transmitters are idealized and optimized, providing a high degree of complexity in the structure for data transmission and reception in the PVM system. Owing to its ubiquitous nature (specifically the virtual machine concept) and also because of its simple but complete programming interface, the PVM system has gained widespread acceptance in the high performance scientific computing community [WWW 02], (Werstein et al., 2003; Araiijo et al., 2003; Mattson, 1995).

#### 2.2.3 Theoretical Chemistry Group Message Passing System (TCGMSG)

TCGMSG is a toolkit for writing portable parallel programs using a message passing model. This message passing harness was written by Robert Harrison et al. of Battelle Pacific Northwest National Laboratory, USA (previously at Daresbury Laboratory and Argonne National Laboratory). Supported are a variety of common UNIX workstations, mini-super and super computers and heterogeneous networks of the same, along with true parallel computers such as the Cray T3D/E, IBM SP, Intel Paragon, the Kendall Square Research KSR-2, and several others. Applications port between all of these environments without modification to the parallel constructs [WWW 03], (Mattson, 1995).

#### 2.2.4 AVS/Express Parallel Edition

AVS/Express Parallel Edition harnesses the power of multi-processor and networked computers for high-performance tasks by permitting distributed computation across shared memory or clustered processor architectures. AVS/Express Parallel Edition allows any combination of devices and platforms to contribute to the most demanding rendering and processing challenges. AVS/Express has been successfully deployed in a wide range of high performance implementations that demand the highest levels of processing power, reliability and flexibility [WWW 04]. The distributed shared memory also known as virtual shared memory (VSM) or partitioned global address space (PGAS) approach is built around a familiar paradigm for writing parallel programs; multiple processes interacting with and communicating by means of shared memory. It frees a programmer from having to deal explicitly with data exchange, and therefore, provides an easier method of programming. The DSM library is responsible for memory consistency maintenance and ensures each process has access to the most recent version of data. The best known products of this type are SCAI's TCP-Linda® and Paradise® systems [WWW 06], (Mattson, 1995), TreadMarks (Keleher et al., 1994), SCASH (Harada et al., 1999), UPC [WWW 05], [WWW 14], (Husbands & Yelick, 2007; Cantonnet et al., 2004), CORSO [WWW 15], and Cluster OpenMP\* for Intel® C++ Compiler [WWW 07], (Buchau et al., 2008).

The DSM approach has number of noticeable benefits: (1) It is very simple to learn and to use, enabling existing programs to be parallelized rapidly and new ones to be developed easily; (2) It makes creating portable programs much less complicated, since architecture-specific low-level details are hidden from the user; (3) It enables advanced parallel execution features like dynamic load balancing to be implemented easily (Werstein et al., 2003; Gansterer & Zottl, 2005).

#### 2.3.1 TCP-Linda

$\mathbf{2.3}$

TCP-Linda, introduced in the mid of 1980's, was the first commercial product to implement DSM for large workstation clusters and supercomputers. TCP-Linda is a proven industry standard for parallel programming and is well known for its reliability and efficiency. TCP-Linda provides a single, logically shared memory to all of the processes in a parallel program.

Each process sees the same data space, and it can read or write shared data by using simple operations, *in* and *out*, respectively. No process ever has to worry about directly communicating with any other process; all such low level operations are handled by the system itself. The DSM works in this way regardless of whether it resides physically in a single memory, or it is actually distributed among the various processors participating in a program execution. TCP-Linda also differs from message passing in that it includes high-level coordination languages for parallel programming. It adds functionality to a standard programming language like C, C++, or FORTRAN for managing ensembles of independent processes, usually via a small set of simple operations which programmers use to implement parallelism [WWW 06], (Mattson, 1995).

#### 2.3.2 Unified Parallel C (UPC)

UPC [WWW 14], (Gansterer & Zottl, 2005; Husbands & Yelick, 2007; Brightwell & Wen, 2004; Cantonnet et al., 2004; Patel & Gilbert, 2008) is a parallel extension of the C standard for distributed shared memory computers. UPC is an example of the Partitioned Global Address Space (PGAS) model that offers a global view of computation to the programmer. It supports high performance scientific applications. In the UPC programming model, one or more threads are working independently, and the number of threads is fixed either at compile time or run-time. Memory in UPC is divided into two spaces: (1) a private memory space and (2) a shared memory space. Every thread has a private memory that can only be accessed by the owning thread. The shared memory is logically partitioned and can be accessed by every thread. To improve the performance of memory accesses, UPC introduces the concept of thread affinity. With this feature, UPC optimizes memory-access performance between a thread and the per-thread address space where the thread has been bound.

In UPC, workload management is implicit, while workload partitioning and worker mapping can be either implicit or explicit. Implicit workload partitioning and task mapping are supported through an API called *upc\_forall* which is similar to *for* iteration in C programming, except that the content of the iteration will be run in parallel. When this API is used, there is no need for additional programming effort for programmers to map the task to threads. The explicit approach in UPC for workload partitioning and worker mapping is similar to the one in MPI, where programmers have to specify on what will be run by each threads. In UPC, communication among threads adopt the Partitioned Global Address Space (PGAS) paradigm by making use of pointers. There are three types of pointer commonly used in UPC: (i) private pointer where the private pointers point to their own private address space, (ii) private pointer-to-share where the private pointers from one address space point to the other shared address space.

#### 2.3.3 Intel® Cluster OpenMP\* (CLOMP)

In May 2006, Intel Corporation introduced the new Cluster OpenMP standard [WWW 07]. It is based on OpenMP and supports distributed memory cluster computers. In a first step, it appears to the software developer in the same way as classical OpenMP. One process is started and threads are created in the parallel section of the program. These threads are distributed among the computing nodes [WWW 07]. All threads see the same virtual shared memory. For efficiency purposes, data must be declared sharable or not. If a thread writes to a memory page, all other threads on the other nodes are noticed about this action. If a thread reads a memory page, it is checked to be up-to-date and data is exchanged where required. To keep data transfer to a minimum, it is necessary to read and write data in a very ordered way.

Cluster OpenMP is used to distribute the threads among the computing nodes. If a node has multiple processors or multicore CPUs, classical OpenMP distributes the load of a Cluster OpenMP thread with classical threads among the processors of a node (Buchau et al., 2008; Wong & Rendell, 2007).

#### 2.3.4 CORSO

CORSO is a representative of the shared object based (SOB) model and is a platform independent middleware. The SOB model is a subtype of the VSM model. A central idea of the space based concept is to have a very small set of commands for managing the objects in the space. Originally CORSO was developed at Vienna University of Technology, now a commercial product, produced by Tecco [WWW 15]. CORSO supports programming in C, C++, Java, and .NET. In a CORSO run-time environment, each host contains a Coordination Kernel, called CoKe. It communicates with other CoKe's within the network by unicast. Noticeable important features of CORSO are: (1) processes can be dynamically added to or removed from a distributed job during execution. Thus, this feature makes CORSO an attractive platform for dynamically changing grid computing environments, (2) CORSO distinguishes two types of communication objects: Const objects can only be written once, whereas var objects can be written an arbitrary number of times, (3) for caching, CORSO provides the *eager mode*, where each object replication is updated immediately when the original object was changed, and the *lazy mode*, where each object replication is only updated when it is accessed, (4) CORSO comprises two transaction models, hard-commit (in case of failure, the transaction aborts automatically without feedback) and *soft*-commit (the user is informed if a failure occurs) [WWW 15].

### 2.4 DM Vs. DSM - Comparative Performance on a HPC Cluster

Parallel computing provides a method to increase the performance of computationally intensive tasks by distributing their computation across multiple processors. Inter process communication can be provided through the libraries based on the message passing paradigm, in particular the MPI and PVM, or through the abstraction of a single memory address space available to all processes, known as DSM, in particular the TCP-Linda, UPC, CLOMP, CORSO, and Treadmarks.

Performance evaluation and comparison of representatives of two important parallel programming paradigms, the message passing model and the DSM model, have been studied by several authors.

#### 2.4.1 Performance Comparison of Treadmarks, PVM, and MPI

TreadMarks DSM system has been compared with the message passing systems, parallel virtual machine (PVM), and message passing interface (MPI) by Werstein et al. (2003). Three main classes of parallel problems, namely, synchronous, loosely synchronous, and embarrassingly parallel have been selected for the case study. Training of back-propagation neural network, Mergesort and Mandelbrot set programs are chosen to represent the main class of parallel problems, in that order. The performance tests have been made on a cluster of 32 Intel Pentium III nodes.

For the MergeSort parallel algorithm, all three libraries show poor performance. The complexity of this problem is  $n \log n$  which is similar to the complexity of communication. This causes communications between nodes to override the increased performance of additional nodes. When increasing the numbers to be sorted only the MPI shows any improvement as nodes are added. While PVM maintains a constant performance, the performance of the DSM degrades rapidly. This is due to virtual memory paging overhead. While the MPI program only shows a small increase in performance, the DSM program shows a major improvement when the amount of available memory is increased. But when the number of nodes increases, the DSM program still shows poor performance compared to the message passing programs. Profiling of the libraries shows that the DSM program generates significantly more network traffic than the message passing libraries. For the Mandelbrot set parallel algorithm, all three libraries had shown similar performance. However MPI had the best overall performance. PVM also had a better speedup than DSM. The speedup scales almost linearly up to 24 nodes. After that point, additional nodes had resulted in decreasing performance. The near linear speedup reflects the embarrassingly parallel nature of this problem. The DSM program consistently generates approximately twice as much network traffic as the message passing programs. Thus it avoids the accelerating increase in data exchanged which is the main cause of its poor performance, especially with a high number of nodes, for the Mergesort and NN programs.

In the training of back-propagation neural network parallel algorithm, two data sets have been used to train the neural network. The first is the shuttle data set drawn from sensor data recorded during NASA space shuttle mission. The neural network is a three layer  $9 \times 40 \times 1$  network. The second training data set is the forest cover data set. The neural network is required to determine the type of forest cover. The neural network is a three layer  $54 \times 160 \times 1$  network.

With the shuttle data set, both message passing libraries show better performance. The speedup occurs almost linearly up to sixteen nodes before falling off to achieve a speedup of approximately 21 and 23 with 32 nodes for PVM and MPI, respectively. DSM performs well up to 8 nodes after which its speedup drops to less than one. With the forest data set, MPI shows the best performance with a speedup of 21 on 32 nodes. PVM performs similarly to MPI up to 24 nodes before slowing down a little on 32 nodes. DSM performs comparatively better obtaining a reasonable speedup with up to 16 nodes then reducing to a speedup of 3 with 32 nodes.

The slowdown of the DSM program is primarily due to the increase in network traffic which saturates the network. As the number of nodes is increased the volume of network traffic also increases. In message passing libraries, this increase is linear, but, in DSM, this leads to an exponential increase in the amount of data being transmitted for the neural network application. The reason for the reduced performance of the PVM version of the neural network compared to MPI version is due to the poor performance of the broadcast operation of PVM. The broadcast time for PVM is significantly higher than that for MPI.

#### 2.4.2 Performance Comparison of UPC, CORSO, and MPI

Gansterer & Zottl (2005) have also studied the performance comparisons between the message passing (MP) paradigm and the DSM/PGAS paradigm. MPI and UPC/CORSO [8] have been

chosen for the implementation of the MP model and the DSM/PGAS model, respectively. UPC is a parallel extension of the ANSI C standard for PGAS model. In the UPC programming model, one or more threads are working independently, and the number of threads is fixed either at compile time or at runtime. CORSO is a representative of the SOB model. SOB (shared object based) model is a subtype of the DSM model. In this concept, objects are stored in a space. In CORSO, processes can be dynamically added to or returned from a distributed job during execution. Such dynamic allocation or deallocation cannot be implemented either in MPI or in UPC.

Three benchmark tests have been implemented in MPI, UPC, and CORSO: (i) two classical summation formulas for approximating  $\pi$ , (ii) a tree structured sequence of matrix multiplications, and (iii) the basic structure of the eigenvector accumulation. Because of the simple dependency structure (only two synchronization points) of  $\pi$  approximation, it is easy to parallelize and allows one to evaluate the overhead of managing shared objects in comparison to explicit message passing. In the parallel implementation of this problem, each processor computes its partial sum, and then finally all the partial sums are accumulated on one processor.

In the sequence of matrix multiplications, owing to its tree structure, it involves much more communication than benchmark(i) and is harder to parallelize. If the number of processors  $(N_P)$  allocated to benchmark(ii) is a power of 2, the binary tree is balanced, this leads to better utilization of the processors involved than for an unbalanced tree. Benchmark(iii) has the structure of a binary tree with matrix multiplications at each node. However, in contrast to benchmark(ii), the size of the node problems increase at each stage, this leads to a much lower computation per communication ratio. This makes it the hardest problem to parallelize.

For the benchmark(i), owing to the high degree of parallelism available, the speedup values of all three implementations are relatively high. However, DSM implementations show lesser performance than message passing paradigms. In benchmark(ii), for a balanced binary tree, the utilization of active processors is maximal, and therefore the speedup curve shows an oscillating pattern. Owing to the master-worker implementation, the speedup value and the execution time for one processor and for two processors are equal. For benchmark(iii), the speedup values are disappointingly low for all three implementations (in some cases, even a slowdown occurs). This reflects the difficulty of parallelizing benchmark(iii) - in particular, its low computation per communication ratio. Therefore, the implementations in the DSM/PGAS model for the all three benchmarks achieve somewhat lower performance than explicit message passing programs.

#### 2.4.3 Performance Comparison of CLOMP and OpenMP

Intel Corporation's Cluster OpenMP (CLOMP) standard transforms a computer cluster with DM into a DSM system.

Buchau et al. (2008) have compared the CLOMP and OpenMP. CLOMP is used to parallelize a boundary element method based on the fast multipole method. Efficiency is studied for electrostatic field problems. The results of the novel CLOMP approach are compared with the classical OpenMP.

In this exercise, a system of linear equations is solved iteratively and a matrix vector product is computed in each iteration step. This product is accelerated by the fast multipole method. The number of operations, which must be evaluated, is relatively small. However, a relatively large amount of data must be interchanged.

Two numerical examples have been studied to analyze the efficiency of OpenMP and Cluster OpenMP in the context of a boundary element method (BEM) with the fast multipole method (FMM). The first example is an electrostatic field problem. A linear system of equations with 81688 unknowns is obtained. A classical BEM approach would result in memory requirements of 50GB. The FMM compresses the matrix to 500MB.

A second numerical example investigates the steady currents inside a printed circuit board (PCB). The PCB was discretized with second order quadrilateral elements and the resulting linear system of equations for the 86453 unknowns is solved. This would require 56GB of main memory with a classical BEM. The application of the fast multipole method reduces this amount to 900MB.

Two different computers have been used for the numerical solution of these two examples. One computer was equipped with 16 Intel Itanium 2 processors with a clock speed of 1.3 GHz. The other computer cluster consisted of eight computing nodes where each node had two AMD opteron processors with a clock speed of 2.2 GHz. To determine the speedup of parallelization, a serial reference program run was run.

Speedup related to matrix assembly and solution of linear system of equations in the case of OpenMP and Cluster OpenMP have been presented. The speedup for matrix assembly was excellent. Even for 16 threads the speedup was 15.8. Unfortunately, the speedup for solution of the system of linear equations was much worse. Memory bandwidth was only one factor.

Since a DM computer causes communication overhead between the virtual threads, the efficiency of Cluster OpenMP was shown to be worse than the efficiency of OpenMP. Even in the case of matrix assembly, the speedup for 4 threads, which ran on 2 computing nodes, is only 3. One reason is that after each writing to memory, the other computing node has to be informed about this change in the DSM. The speedup for the solution of the linear system of equations is good in comparison to OpenMP. One reason, has been that the FMM algorithm was slightly modified in this scenario. Some fast operations were done in each thread. Hence, data was locally available and was not required to be transferred between the computing nodes.

Finally, the authors concluded that Cluster OpenMP is a promising approach to cluster computers. Particularly, as parallelization is easy to be carried out. Both OpenMP and Cluster OpenMP were recognized as good choices for an easy and efficient parallelization. Especially the combination of parallelization with a fast efficient method like that of BEM with the FMM was very attractive.

#### 2.4.4 Performance and Flexibility of MPI and UPC

The choice of the parallel language has a major impact on the productivity of the HPC development process. A set of quantifiable criteria, defines a set of hypotheses based on commonly held beliefs, and evaluates them empirically with statistical tests, was selected (Patel & Gilbert, 2008). The comparison criteria are variables such as performance that are measurable with well-defined metrics such as program speedup and run time. Then, the hypotheses are statistically validated using the data from the human-subject experiments conducted as part of the DARPA High Productivity Computing Systems (HPCS) program.

This approach has been applied to empirically compare message passing (using MPI) and partitioned global address space (using UPC) programming models. Two key contributions have been made: (i) it presents a general approach to comparing parallel programming models using rigorous statistical hypothesis tests, and (ii) it presents novel hypotheses for comparing the performance and productivity of the MPI and UPC programming languages, validates them using empirical data, and analyzes the statistical results.

Data has been collected from the HPCS classroom productivity studies conducted at UCSB in 2006 and 2007, to validate the hypotheses. Parallel implementations with MPI and UPC for

power method have been developed. The power method is an iterative procedure that finds the largest absolute eigenvalue and the associated eigenvector of a matrix. The IMB MPI/C compiler and the Berkeley UPC compiler have been used for development.

Test results have shown to validate some of the commonly held beliefs about parallel programming models. MPI programs had lower run times compared to UPC, confirming the conventional wisdom. When both MPI and UPC programs achieved similar parallel speedup and scaling behavior on average, a higher variation in the performance of UPC programs has been observed. Analysis shows that this is because different design choices for parallelization in UPC being lead to significantly different performance results. Developing a parallel program for a problem in the PGAS model requires comparatively less effort. This is validated by the result that UPC programs require less code and thereby less effort compared to MPI.

In the analysis, several UPC solutions which had correctness and performance problems that typically do not manifest themselves at the scale of development tests were found (Patel & Gilbert, 2008). This leads them to believe that PGAS languages should be equipped with profiling capabilities that can optimize accesses to the global address space.

## Chapter 3

# Extracting Parallelism from a Hierarchy of Processing Levels in a Cluster

### 3.1 Mixed Mode Approach for HPC Cluster Programming.

Shared memory models have been more prominent in the conventional super computing domain where uniform memory access (UMA) and non-uniform memory access (NUMA) architectures have existed (Robertson & Rendell, 2003), but have recently emerged as symmetric multiprocessors (SMP), where a smaller number of CPUs also have access to a single memory space. Further, manufacturers have increasingly used clustering of SMP systems together to build powerful platforms. By utilizing a mixed mode programming model there is a possibility of taking advantage of the benefits of both shared memory and distributed memory models.

The majority of mixed mode applications involve a hierarchical model; MPI parallelization occurring at the inter-node level, and OpenMP/POSIX threads parallelization occurring at intra-node level. Whilst the majority of mixed mode programs implement this type of model (Smith & Bull, 2001), a number of authors have described non-hierarchical models (Smith & Bull, 2001; Bova et al., 2000). For example, message passing could be used within a code when it is relatively simple to implement and shared memory parallelism used where message passing is difficult.

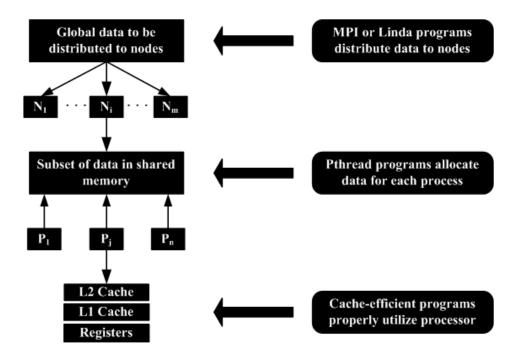

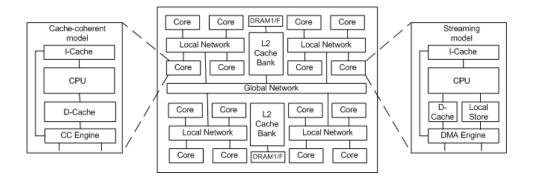

Figure 3.1 shows the memory hierarchy of a typical HPC cluster. Mainly, a number of nodes are connected by a high-speed network where, within each SMP node there may be many processors; along with each processor's memory access being either to a high speed cache memory or the low speed main memory.

Message passing programming code written in MPI is obviously portable and should transfer

Figure 3.1: Mixed mode programming model on HPC cluster Ref. (Wu et al., 2002).

easily to clustered SMP systems. Inside each MPI process there may be three choices: (i) use POSIX threads for creating threads, one or more threads may belong to the MPI process mapped to the SMP node; (ii) use shared memory model such as OpenMP to provide a more efficient parallelization strategy within an SMP node; (iii) use MPI for local processes mapped to all processors of the each node. Finally, inside each process to use different algorithms that utilize the cache.

#### 3.1.1 Mixed mode MPI/OpenMP algorithms

Smith & Bull (2001) have studied the benefits of developing mixed mode MPI/OpenMP applications on both single and clustered SMPs. The following various situations where a mixed mode code may be more efficient than a corresponding pure MPI implementation, whether on an SMP cluster or on a single SMP system, are discussed: codes which scale poorly with MPI (load balance and fine grain parallelism problems); replicated data; ease of implementation; restricted MPI process applications; poorly optimized intra-node MPI; poor scaling of the MPI implementation; and computational power balancing.

The code for *Game of life* problem has been chosen as a case study. This problem is a simple grid based one, which demonstrate complex behavior. It is a cellular automaton where the world is a 2D grid of cells which have two states, *alive* and *dead*. At each iteration the new state of the cell is entirely determined by the state of its eight nearest neighbors at the previous iteration.

The performance of the two OpenMP codes, OpenMP (SMPD) and OpenMP (Loop), and MPI code have been measured with two array sizes,  $100 \times 100$  and  $700 \times 700$ , respectively, for 10,000 iterations. The code was run on a Sun HPC 3500 system with exclusive access. This system had 8400 MHz UltraSparc II processors and 8 Giga bytes of memory running Solaris 2.7. Both the OpenMP codes had shown better performance than the MPI code on both problem sizes.

Thus developing a mixed mode MPI/OpenMP code may give better performance than the pure MPI code, and would therefore be more suited to an SMP cluster. Therefore three mixed mode versions of the code have been developed: (i) loop based OpenMP/MPI; (ii) 2D OpenMP/MPI; and (iii) SPMD OpenMP/MPI. The performance of three codes have been measured with the same array sizes for the same number of iterations. comparisons of these mixed code with the pure MPI implementation reveals a performance improvement have been obtained: the over all timings have reduced and the scaling of the code with increasing thread number is better.

Even when a pure OpenMP implementation gives better performance over a pure MPI implementation, this does not always mean that a mixed MPI/OpenMP code will give better performance than a pure MPI implementation. For example by implementing the mixed mode code with the MPI parallelization above the OpenMP parallelization, as is often the recommended case owing to the lack of a guaranteed thread-safe MPI implementation, extra synchronization is often introduced, which can reduce the performance. For this particular example the mixed mode code needed to be written with MPI and OpenMP at the same level, rather than using the more common hierarchical model. This creates issues with portability, relying on threadsafe MPI implementation, and adds to the code complexity, but increases performance.

Mixed mode programming style will not always be the most effective mechanism on SMP systems and cannot be regarded as the ideal programming model for all codes. Benefits may be obtained under the following MPI code environments: (i) poor scaling with MPI processes due to load imbalance or too fine a grain problem size; (ii) from memory limitations due to the use of a replicated data strategy; and (iii) from a restriction on the number of MPI processes combinations. Further more, if the system suffers from a poorly optimized or limited scaling MPI implementation, then a mixed mode code may increase the code performance.

#### 3.1.2 Mixed mode MPI/pthreads and MPI/cache algorithms

Different types of matrix multiplication algorithms on system having multiple memory layers to show how performance is affected in mixed mode programming without a good cache algorithm, even when the work load is perfectly balanced, were used (Wu et al., 2002). The cache layer matrix multiplication algorithms such as *simple three loops* algorithm, *blocking C* algorithm, *blocking A* algorithm, *transform and blocking A* algorithm, *recursive* algorithm, and *Strassen's* algorithm have been used in their case study, which vary from those that have high cache misses to those that effectively use cache. *Overlapping matrix B*, *non-overlapping*, *blocking*, and *transform and blocking* and *Cannon's* matrix multiplication algorithms are chosen for the SM layer. Two dimensional *broadcasting* and *Cannon's* matrix multiplication algorithms are implemented in Pthreads and in MPI, respectively. In the mixed mode programming model, MPI is used for the communication between global nodes and, within each MPI node Pthreads are used for creating one or more threads.